SPI Interface¶

The SPI interface gives access to all features of the CRMXchip. The interface consists of five 3.3V digital signals:

-

IRQ – Interrupt signal. Active low, configurable through the interrupt mask register

-

CS – SPI Chip select, active low

-

SCK – SPI clock input

-

MOSI – SPI data input

-

MISO – SPI data output

Interface description¶

Bit and byte order¶

The data on the SPI bus is clocked with most significant bit first. All multi-byte register data are sent in big-endian byte order.

Clock polarity¶

Data is valid in the low-to-high transition of SCK. This is also known as the clock being active high with valid data on the leading clock edge.

Maximum clock speed¶

The maximum clock speed supported by TiMo is 2MHz. Clock speeds above this limit may result in unexpected behavior.

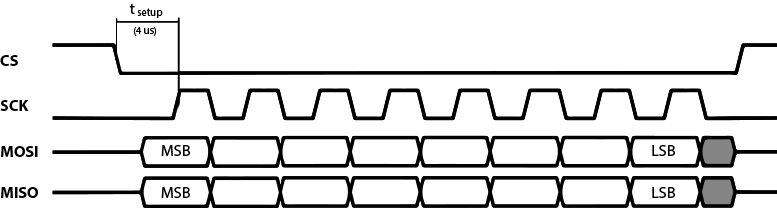

Setup time¶

The SPI slave unit has a setup time of 4 μs after the high-to-low transition of the CS signal.

SPI operation¶

SPI transactions¶

All SPI transactions start with a high-to-low transition on the CS pin. The CS pin must be held low during the entire SPI transaction.

The IRQ_FLAGS register is always shifted out as the first byte of each transaction.

Example SPI transaction

Example SPI transaction

SPI commands¶

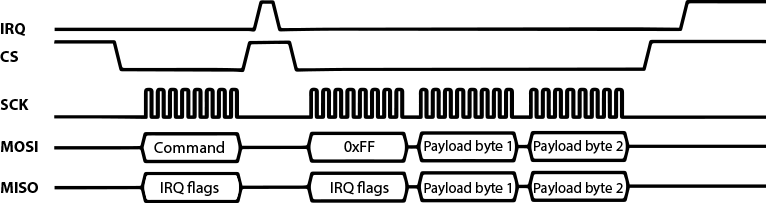

All SPI command sequences, except for the NOP command, consist of two SPI transactions. The first transaction shall be one byte long, this is the command byte. The second transaction is the payload. The second transaction must not be started until the TiMo module has confirmed the command by a high-to-low transition on the IRQ pin. The first byte being sent to TiMo in the second transaction will be ignored, however it is suggested this byte is being sent as 0xFF. See below for an example full SPI command sequence.

NOTE: Bit 7 in the IRQ flags register MUST be observed. A ‘1’ in this bit means that the SPI slave module is unable to process the current transaction, and the full command sequence MUST be restarted – this means sending the command transaction again.

Example SPI command sequence with a pending IRQ when sequence started

Example SPI command sequence with a pending IRQ when sequence started

The available SPI commands are listed in the table below.

| Command | Binary value | Comment |

|---|---|---|

| WRITE_REG | 01AA AAAA | Write to a register. AAAAAA = 6 bit register address. |

| READ_REG | 00AA AAAA | Read from a register. AAAAAA = 6 bit register address. |

| READ_DMX | 1000 0001 | Read the latest received DMX values from the window set up by the DMX_WINDOW register. |

| READ_ASC | 1000 0010 | Read the latest received ASC frame. |

| NOP | 1111 1111 | No operation. Can be used as a shortcut to read the IRQ_FLAGS register. |

Register map¶

All undefined bits in the table below shall be considered reserved for future use - don't care when read, write as 0.

Do not read or write undefined registers – doing so could result in undefined behavior.

| Address (hex) | Mnemonic | Bit no. | Type | Reset value | Description |

|---|---|---|---|---|---|

| 00 | CONFIG | Configuration register | |||

| UART_EN | 0 | R/W | 1 | Enable UART output of DMX frames (required for RDM). 0 = Disabled, 1 = Enabled |

|

| Reserved | 1-6 | - | - | Reserved for future use | |

| RX_ENABLE | 7 | R/W | 1 | Enable wireless DMX operation. 10 = Enabled, 0 = Disabled |

|

| 01 | STATUS | Status register | |||

| LINKED | 0 | R/W | - | 0 = Not linked, 1 = Linked to TX (or pairing) Write 1 to unlink |

|

| RF_LINK | 1 | R | 0 | 0 = No radio link, 1 = Active radio link | |

| DMX | 3 | R | 0 | 0 = No DMX available, 1 = DMX available | |

| Reserved | 4-6 | - | - | Reserved for future use | |

| UPDATE_MODE | 7 | R | 0 | 0 = chip operational, 1 = In driver update mode | |

| 02 | IRQ_MASK | IRQ mask register | |||

| RX_DMX_IRQ_EN | 0 | R/W | 0 | Enable DMX frame reception interrupt | |

| LOST_DMX_IRQ_EN | 1 | R/W | 0 | Enable loss of DMX interrupt | |

| DMX_CHANGED_IRQ_EN | 2 | R/W | 0 | Enable DMX changed interrupt | |

| RF_LINK_IRQ_EN | 3 | R/W | 0 | Enable radio link status change interrupt | |

| ASC_IRQ_EN | 4 | R/W | 0 | Enable alternative start code interrupt | |

| Reserved | 5 | - | - | Reserved for future use | |

| EXTENDED_IRQ_EN | 6 | R/W | 0 | Enable extended interrupts | |

| Reserved | 7 | - | - | Reserved for future use | |

| 03 | IRQ_FLAGS | IRQ flags register | |||

| RX_DMX_IRQ | 0 | R | 0 | Complete DMX frame received interrupt | |

| LOST_DMX_IRQ | 1 | R | 0 | Loss of DMX interrupt | |

| DMX_CHANGED_IRQ | 2 | R | 0 | DMX changed in DMX window interrupt | |

| RF_LINK_IRQ | 3 | R | 0 | Radio link status change interrupt | |

| ASC_IRQ | 4 | R | 0 | Alternative start code frame received interrupt | |

| Reserved | 5 | - | - | Reserved for future use | |

| EXTENDED_IRQ | 6 | R | 0 | Extended interrupt | |

| SPI_DEVICE_BUSY | 7 | R | 0 | SPI slave device is busy and cannot comply with command. Command sequence MUST be restarted. | |

| 04 | DMX_WINDOW | Status register | |||

| WINDOW_SIZE | 0-15 | R/W | 512 | Length of DMX window | |

| START_ADDRESS | 16-31 | R/W | 0 | Start address of DMX window | |

| 05 | ASC_FRAME | ASC frame info register | |||

| START_CODE | 0-7 | R | 0 | Start code of received ASC frame | |

| ASC_FRAME_LENGTH | 8-23 | R | 0 | Length of received ASC frame (0-512) | |

| 06 | LINK_QUALITY | Radio link quality register | |||

| PDR | 0-7 | R | - | Packet delivery rate (display as %) 0 = 0%, 255 = 100% |

|

| RSSI | 0-7 | R | - | Average link RSSI 0 = 0 dBm, 40 = -20 dBm (strong link), 200 = -100 dBm (weak link) |

|

| 0A | EXTENDED_IRQ_MASK | Extended IRQ mask register | |||

| Reserved | 0-5 | R/W | - | Reserved for future use | |

| UNIV_META_CHANGED_EN | 6 | R/W | 0 | Enable universe metadata changed interrupt | |

| Reserved | 7-31 | R/W | - | Reserved for future use | |

| 0B | EXTENDED_IRQ_FLAGS | Extended IRQ flags register | |||

| Reserved | 0-5 | R | - | Reserved for future use | |

| UNIV_META_CHANGED | 6 | R/W | 0 | Universe metadata changed | |

| Reserved | 7-31 | R/W | - | Reserved for future use | |

| 10 | VERSION | Version register | |||

| FW_VERSION | 0-31 | R | - | Firmware software version | |

| HW_VERSION | 32-63 | R | - | Hardware revision | |

| 21 | LINKING_KEY | Linking key register | |||

| CODE | 0-63 | W | - | Linking key 8 digit code | |

| MODE | 64-71 | W | - | Mode of transmitter 0 = CRMX Classic 1 = CRMX2 |

|

| UNIVERSE | 72-79 | W | - | Universe number to link to. Corresponds to Stardust's output numbers. | |

| 33 | UNIVERSE_COLOR | Universe Color Register | |||

| RGB_VALUE | 0-23 | R | - | 24 bit RGB value for the universe color. | |

| 37 | UNIVERSE_NAME | Universe Name Register | |||

| UNIVERSE_NAME | 0-128 | R | - | 16 character string, null terminated. | |

| 38 | TEMP_LINKING_KEY | Temporary, non-persistant linking key register | |||

| CODE | 0-63 | W | - | Linking key 8 digit code | |

| MODE | 64-71 | W | - | Mode of transmitter 0 = CRMX Classic 1 = CRMX2 |

|

| UNIVERSE | 72-79 | W | - | Universe number to link to. Corresponds to Stardust's output numbers. |

Interrupts¶

The IRQ pin is used to indicate that there is one (or more) pending interrupt that has been enabled through the IRQ_MASK register. The IRQ pin is also used to indicate that the SPI slave is ready to receive the second transaction of an ongoing SPI command sequence.

The IRQ pin will always go high (inactive) after a successful SPI transaction. If any interrupts are pending, or when the chip is ready for the second transaction in a SPI command sequence it will be indicated through a high-to-low transition on the IRQ pin.

RX_DMX_IRQ¶

Asserted when a complete DMX frame has been received. Cleared by issuing a READ_DMX command sequence.

LOST_DMX_IRQ¶

Asserted when DMX stream is lost. This may be an effect of losing radio link, or if DMX stream in to the transmitter is terminated (for instance the DMX cable to the transmitter is unplugged). Cleared by reading the STATUS register.

DMX_CHANGED_IRQ¶

Asserted when a complete DMX frame has been received and any slot within the DMX window has changed value. Cleared by issuing a READ_DMX command sequence.

RF_LINK_IRQ¶

Asserted whenever the state of the radio link has changed. This may be:

-

radio link is lost

-

radio link is established

-

receiver got paired to transmitter

-

receiver got unpaired from transmitter

Cleared by reading the STATUS register.

ASC_IRQ¶

Asserted when a complete ASC frame has been received. Cleared by reading the ASC_FRAME register.

DMX Window register¶

The DMX_WINDOW register is used for setting up the DMX window filtering function. Please refer to the section about DMX window on page 20 for more details.

Hardware revision¶

Hardware revision is a 32bit number that shall be translated into a string. It indicates the revision number of the TiMo module. For instance the 32 bit value in hexadecimal form 0x000A0001 corresponds to module revision “000A0001”.

Firmware version¶

The firmware version is a 32bit value that shall be translated into a string on the form X.Y.Z.Y where X is the most significant byte of the 32 bit version number and Y is the least significant byte. For instance the 32 bit value 0x01000103 shall be presented as 1.0.1.3 on any UI or in any written representation.

Linking Key¶

Writing the linking key register initiates the linking process using a linking key.

The following information is written:

- Code: An 8 digit key code.

- Mode: The operating mode of the transmitter: CRMX2 or CRMX Classic.

- Universe: The universe number of the link to link to.

Code¶

The code is an 8 digit code encoded into 8 bytes. For example 12345678 is written as 0x01, 0x02, 0x03, 0x04, 0x05, 0x06, 0x07, 0x08.

Mode¶

To link properly the mode of the transmitter needs to be written.

0x00: CRMX Classic0x01: CRMX2

Universe¶

This field corresponds to the output numbers of Stardust, but is zero-indexed. If linking to the first output of a Stardust, write 0x00 to this field, 0x01 for Output 2, etc.

Note: In CRMX Classic mode, only every second value (0x00, 0x02, 0x04, 0x06) is available.

If linking to a single universe transmitter, for instance Aurora, only universe 0x00 and CRMX Classic mode is available.

Read more in the Universe metadata section.